Hmm, pa moze i ta varijanta ... A da li moze recimo neka BusPirate varijanta to isto da odradi, mislim programiranje CPLD-ova? Ovaj drugi sto si preporucio je vidim bas ozbiljan ali specifican za te Xilinx/Altera stvari, ja sam pocetnik u tome mozda mi je to "premnogo". Ovaj BusPirate bi mogao i za jos neke stvarcice da iskoristim ako moze to sve da se odradi sa njim.

Inace za ovu konkretnu realizaciju sa CPLD, hmm, ne znam sta sve treba, poenta je da SPDIF pretvorim u "nesto" sto mogu najlakse i najbrze da prebacim u drugi CPU, mozda kao SPI ili cak paralelni neki port, bilo sta zasta mi treba malo procesorkosg vremena da iscitam. Mislim ako tako gledam onda mi je najlakse da uzmem gotove IC za to da se ne mlatim sa CPLD, recimo

http://www.ti.com/lit/ds/symlink/dir9001.pdf

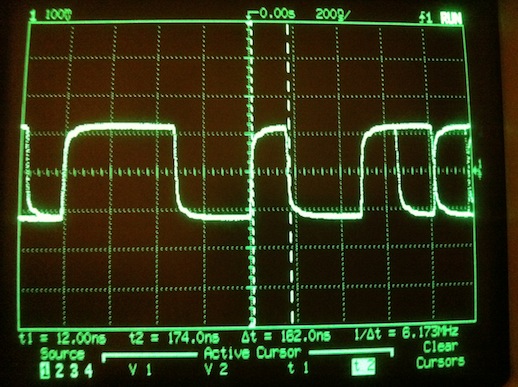

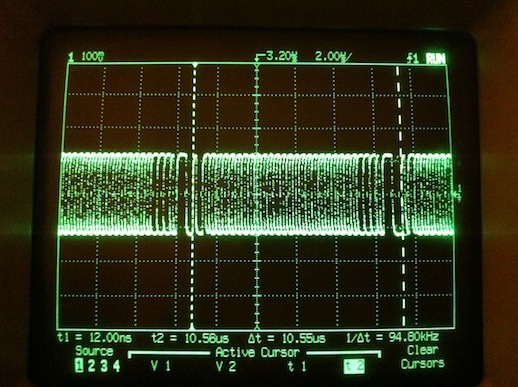

I da to da spomenem, ovde kod SPDIF ima vazdan nekih peripetija sa CLOCK-om, eto bar to mogu da obezbedim (ako moze nesto da olaksa), bilo koju ucestanost u Hz tacnu (do 3 nezavisna izlaza) i to vrlo stabilnu sa veoma malim jitterom. Zato sam i davao one gore linkove sa HW implementacijom, mozda te stvari mogu da se iskombinuju sa nekim klasicnim logickim kolima pa tako malo "pripremljeno" da udjem u CPU za dalju obradu, bar clock i data razdvojeno da imam.

Stavi se FF i ustelu je se R/C za vreme, ovde recimo konstantno za 48k, i razdvoji clk i dat. Posto vec imam PLL ja mogu da upravljam sa njim i da imam opciju i za druge sample rate, 96k recimo ili da se fino stelujem na jednoj da budem u sinhronizaciji da nema dropova. Ovaj trenutni PLL sto imam u CPLD tesko da moze da se napravi, opasan je malac (Si5351) za te stvari, ja bez njih odprilike vise nista ne pravim, trostruki clock generator po ceni jednog XO :)

[Ovu poruku je menjao mikikg dana 01.07.2013. u 01:30 GMT+1]

S/PDIF dekoder sa MCU - Manchester Decoder

S/PDIF dekoder sa MCU - Manchester Decoder